# Reprint

## Simulation Analysis of Access Protocol Storage Requirements in a Local Area Network Node Environment

T. Antonakopoulos, J. Koutsonikos, V. Pallios and V. Makios

### The 8th IASTED International Conference on Modelling, Identification and Control

### GRINDELWALD, SWITZERLAND, FEBR. 1989

**Copyright Notice**: This material is presented to ensure timely dissemination of scholarly and technical work. Copyright and all rights therein are retained by authors or by other copyright holders. All persons copying this information are expected to adhere to the terms and constraints invoked by each author's copyright. In most cases, these works may not be reposted or mass reproduced without the explicit permission of the copyright holder.

SIMULATION ANALYSIS OF ACCESS PROTOCOL STORAGE REQUIREMENTS IN A LOCAL AREA NETWORK NODE ENVIRONMENT

T. Antonakopoulos D.Eng., J. Koutsonikos D.Eng., V. Pailios Ph.D and V.Hakios Ph.D University of Patras, Laboratory of Electromagnetics, Patras, Greece

Abstract: Nodal storage limitations in a storeand-forward computer network lead to blocking; moreover in high-speed LANs where time restrictions are critical, they result in degradation of network performance due to loss or retransmission of blocked packets. In this work we consider the Input/Output Packet Buffer (1/0 PB) at the Interface between the Hedlum Access Control (HAC) unit, responsible for the access protocol, and the Bursty Data Module (BDH), responsible for the processing of higher laver protocols. The arrival of packets to the buffer from the MAC follows an interrupted procedure with exponential distribution for the busy and idle times. The arrival interruptions originate from the Access Protocol used for a high speed (144 Hb/s) Integrated Services LAN. Both busy and idle times are expressed in clock time periods with reference to the network speed. The server which represents the interface between the I/O PB and the BDH is also available in interrupt form to idle times. The measured performance for the delay contribution and the buffer size through simulation analysis is also presented in this paper. Finally. a comparison between the implementation and the simulation is carried out allowing the optimum choice of the buffer design parameters through a trade off between the required performance and the hardware implementation.

#### I. INTRODUCTION

The analysis of the buffer and storage facilities in a network node environment has attracted the attention of a large number of studies because it is often one of the critical resource problems. Hany authors have dealt with the study of buffer systems using a number of assumptions for their analysis either concerning the size of the buffer or the type of the arrivals and the servers available to the buffer [1],[2]. Usually the generalized approaches, appearing in the literature, suffer from two major problems:

i) They consider arrival and departure processee which only approximate the practical system and the used implementation techniques.

11) It is considered that the transfer of data at the input of the buffer and the evacuation of the buffer are "instantaneous". This fact in some cases, especially for high speed Local Area Networks, is not true because usually the data transfer process becomes an important factor of the buffer performance.

The analysis presented in this paper originates from the study and implementation of the input/output (I/O) buffer for an Integrated Services Local Area Network (ISLAN) [3]. The I/O buffer in the node structure lies between the module which is responsible for the processing of packets for the communication protocols, from the Data Link Layer up to the Transport Layer, and the module which is responsible for the implementation of the Access Protocol. The Access Protocol module implements a Hybrid Protocol and delivers/accepts packets to/from the buffer following an interrupted Poisson process using a high-speed parallel interface [4],[5],[6]. The buffer delivers/accepts packets to/from the BDH, through a high speed VHX bus, following an interrupted exponential process.

The paper addresses the analysis of the I/O buffer of a node for the Local Integrated Optical Network (LION) currently implemented under the partial financial support of the Commission of the European Communities within the context of the ESPRIT program.

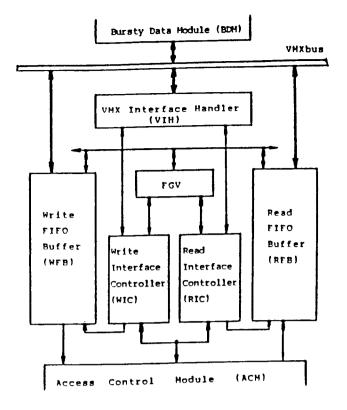

Section II presents the functional block diagram and the critical design/performance parameters of the I/O buffer as well as the details of the buffer interfaces. In Section III the simulation performance analysis of the I/O buffer is presented and finally Section IV presents the discussion of the results obtained in Section III. In Fig.1 the functional block diagram of the I/O PB is depicted. The I/O PB interfaces with the Access Control Manager (ACM), which is responsible for the access protocol implementation, uses two parallel 8-bit buses and the required control signals, one for the Read and one for the Write direction, respectively. The interface speed of 18 Hbytes/sec as well as the 8-bit format are set by the ACH structure.

The I/O FB follows a pipeline pair structure in order to achieve the required high operation speed and the data flow speed adaptation. During the Read channel operation after the ACH notification of the existence of a packet for delivery, the packet is transfered to the Read FIFO Buffer (RFB) under the control of the Read Interface Controller (RIC). After the packet storage the actual length of the packet has been calculated and it is checked with the packet length indicated in the first two bytes of the packet. Then, if the calculated and indicated packet lengths are not the same, the packet is deleted from the RFB otherwise it is kept for further processing. In this way, on the one hand we consume less buffer space and on the other hand we offload both the processing inside the I/O PB and BDH and the VHX bus utilization.

Then, for the valid packets of the RFB, the Frame Check Sequence Generation and Validation (FGV) unit is requested. After FGV acquisition and the indication of a valid packet, the VHX Interface Handler (VHI) requests the VHX bus through an interrupt structure for packet transfer. The FGV operation speed is 8, 16, or 32 (byte, word, longword transfer) times the VHX transfer rate because it is implemented in a serial form.

During the Write channel operation the interface towards the ACH follows the speed and form described in the Read channel operation. In addition the Access Frotocol permits a maximum of four packets to be transmitted per node access, therefore the size of the Write FIFO Buffer (WFB) is four times the maximum packet length. The transfer to the ACH is under the control of the Write Interface Controller (WIC). When there are not four packets in the WFB then the WIC through the VIH generates an Interrupt to the BDH for a transfer of a packet to the WFB. Then the WIC requests the FGV for the FCS sequence generation following the CCITT-32 FCS standard.

In the FGV acquisition and the VHX interrupt generation processes the Read operation has higher priority from the Write operation.

.

Fig.1. The functional diagram of the 1/O Packet Buffer.

For the VHX interface transfers a DHA controller is foreseen with a target speed of 4 Hbytes/sec. The DHA controller is under the control of the BDH which is also responsible for the higher level protocols processing and the users interface [3], [7]. Therefore, for the interrupt handling procedure congestion problem, the I/O PB has one of the highest priorities in the interrupt handling routines supplied by the BDH for the VHX and the BDH internal functions.

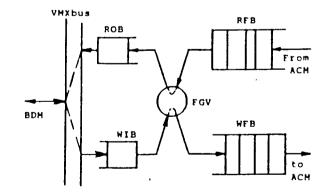

The transfers at the two I/O PB interfaces ( ACH and BDH ) are asynchronous, moreover for each individual interface the transfers of the Write and Read channels are also asynchronous and independent to each other. Therefore, a structure which permits independent and parallel processing of the received and transmitted packets at each interface will speed up the I/O PB function. In addition, at the I/O PB-BDH interface, since the BDH is involved in a large number of processing functions. It is required to offload the handshaking procedures between BDH and the RB, because the VHX interface is not always available for the I/O PB transfers. Therefore, the Write Input Buffer (WIB) and the Read Output Buffer (ROB) are added.

IV. THE SIMULATION PERFORMANCE ANALYSIS OF THE I/O PB.

The simulation model for the I/O PB [8] is shown in Fig.2 and has the following characteristics:

1) The size of the RFB is assumed infinite.

ii) The size of the WFB is four packets.

iii) The VHX bus acquisition from the Read, Write channels and the BDH follows an interrupt procedure where the Read channel has the highest priority and the BDH the lowest. Moreover, the VHXbus is released through a "Release When Done" procedure, therefore when the Read channel, or the Write channel, or the BDH acquires the Bus, any further request is serviced after completion of the work of the current user, following the priority scheme previously mentioned.

iv) The request procedure of the VHX bus for the BDH follows an exponential distribution indicated by busy times (when the BDH requires the VHX) and idle times (when the BDH does not require the VHX) exponentially distributed.

v) For the ACH interface, recarding the Read channel it is considered a busy time period (packets received) and an idle period (no packets received), both exponentially distributed. The same holds for the Write channel, for packets transmission.

vi) The ROB and the WIB are both one packet long.

vil) The operational speeds of the FGV and DHA controler are programmable.

The measured quantities of the I/O PB are:

1) The mean and maximum values of the RFB and WFB.

11) The mean delay for received and transmitted packets (queueing and transmission delay).

111) The FGV utilization by the Read and Write channels.

iv) The VHX utilization by the I/O PB and the BDH.

v) The number of transmitted and received packets.

Fig.2. The simulation model.

The traffic scenario used for the simulation of I/O PB is based on a previous analysis of the hybrid protocol [4] and on the models used in the literature [8], [9] which consider that a node in a network receives twice traffic that delivers to the network. the Considering the LION network [3], [4],[7] for a frame of 5 msec, a network speed of 144 Hb/s and 300 nodes, the reference mean arrival rate for the Read channel is calculated 200 packets/s. The simulation runs for arrival rates between 25 packets to be received and about 200 packets to be transmitted (write channel) for valid simulation results. The network is considered in steady-state which means that the BDH has packets to transmit and the network has packets to deliver to the nodes. The reference time is the hybrid frame and the distribution of the availability of the VHX for transfers between the BDH and I/O PB is taken 40%. 60% and 80% of the hybrid frame duration.

The DHA speeds used are related to the organization of the tranfers and it is 2 MWords/s or 2 MLongwords/s for 16 bit and 32 bit transfers, respectively.

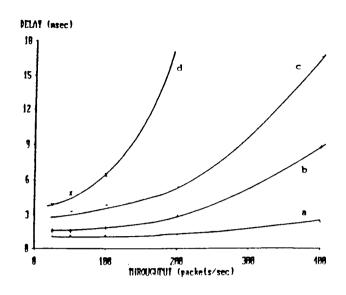

In Fig.3 the throughput-delay performance of the Read channel is presented for the following cases:

|   | DHA speed | VMX availability |

|---|-----------|------------------|

| a | 2HL       | 80%              |

| ь | 2HW       | 801              |

| с | 2HL       | 401              |

| d | 2HW       | 401              |

For the above cases the measured FGV utilization was always less than 10% for the Read channel and its contribution to the total delay was less than 250 usec for a FGV operational speed of 80 Hb/s which is always less than 5% of the total delay. Then the major part of the delay as it is observed in Fig.3 is due to the VHX availability and the DHA speed contribution to the delay is a secondary factor. Taking as a reference the curve "a", the variation of the delay due to the decrease of the DHA speed (curve "b") is much less than the variation of the delay due to the decrease of the VHX availability (curve "c").

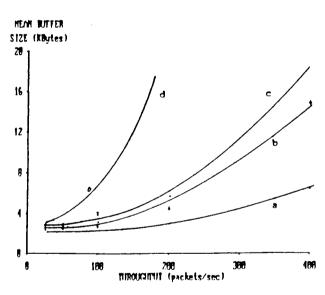

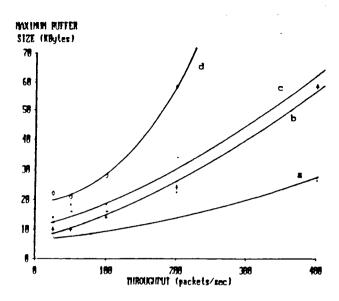

In Fig.4 and Fig.5 the Mean Read Buffer and the Maximum Read Buffer sizes are shown respectively for the cases used in Fig.3. From these figures it is observed that the contribution of the DHA speed and the VHX availability is equivalent (comparing curves "b" and "c" with the curve "a") as far as the

Fig.3. The Read channel Throughput-Delay characteristics.

Flg.4. The Read FIFO buffer mean length.

buffer size is concerned.

•

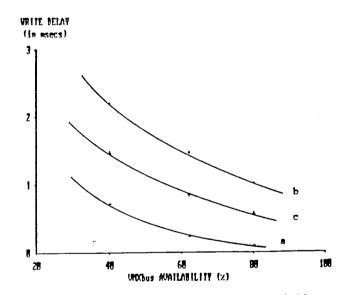

In Fig.6 the Write channel delay is shown versus the VHX bus availability. The delay for the Write channel is measured from the time where the Write channel requests a packet from the BDH until the packet is stored at the WFB. The following curves are depicted:

I) as considers the contribution of the VHX bus availability only to the delay.

Fig.5. The Read FIFO buffer maximum length.

Fig.6. The Write channel Delay characteristics.

ii) b.c: the contribution of the VHX bus availability and the DHA speeds for 2 HWords/s and 2 HLongwords/s, respectively.

From Fig.6 it is observed that for low VHX bus availability the contribution of the DHA speed is equivalent to the contribution of the VHX bus availability. For higher VHX bus availability values, the major contribution to the delay originates from the DHA speed.

400

#### V. DISCUSSION

From the simulation results for the buffer size (Fig.4,5), we can choose the implementation of the DHA at a speed of 2 HWords/s and the RFB at a size of 32 Kbytes (considering the reference mean arrival rate to be 200 packets/sec). From Figures 4, 5, 6, we can observe that through the use of the WIB and ROB we can give the highest priority for the Read channel in the VHX bus interrupt structure, allowing in this way higher VHX bus availability for the I/O PB taking also into account that only useful information is transfered to the BDM ( non valid packets are already rejected internally to the I/O PB).

Finally from the architecture of the I/O PB and the results of Fig.6, we can state that the major contribution in the total packet delay is due to the hybrid protocol [4] and the I/O PB is very efficiently transfering the packets avoiding any bottleneck problems.

#### VI. ACKNOWLEDGHENTS

The authors would like to thank Dr S. Koublas for fruitful discussions and his contribution to the simulation analysis of the I/O PB.

#### REFERENCES

[1] F. Kamoun and L. Kleinrock, "Analysis of Shared Finite Storage in a Computer Network Node Environment Under General Traffic Conditions", IEEE Trans. Commun. Vol. Com-28, Jul. 1980, pp. 992-1003.

[2] H. Bruneel, "Hethod of Analysis for Discrete-Time Buffers with Randomly Interrupted Arrival Stream", IEEE Proceed., Vol. 131, No 5, Sept. 1984.

[3] L. Lambarelli, A. Luvison, D. Roffinella and

H. Sposini, "A High-Performance Hultiservice

Local Communication System" in Proc. IEEE Global

Telecommun. Conf. (GLOBECOH' 85). New Orleans,

LA, Dec. 1985, pp. 457-461.

[4] V. Paillos, T. Antonakopoulos, V. Hakios, "Analysis of the Access Protocol for. a Hultiservise LAN", EURINFO 1988, IFIP European Conference on Information Technology for Organisation Systems, Hay 1988, Athens, Greece.

[5] V. Pallios, T. Antonakopoulos, V. Hakios, "Architecture and Implementation of the Access Hechanism for a Bus-Sructured Huitiservice LAN", 8th International Conference on Distributed Computing Systems, IEEE Computer Society, IEEE, June 13-17, San Jose California, USA. [6] V. Pallios, T. Antonakopoulos, V. Hakios, "A High Speed Access Mechanism for a Huitiservice LAN at 144 Hbs", 8th European conference on Electrotechnics, EUROCON 88, Area Communications, IEEE, EUREL, SER, June 13-17, Stockholm, Sweden.

[7] D. Roffinella, C. Trinchero and G. Fresci, "Interworking Solutions for a Two-Level Integrated Services Local Area Network", IEEE Journal on Selected Areas in Commun., Vol. SAC-5, No. 9, December 1987.

[8] Wayne Graybeal and Udo Pooch, Simulation; Principles and Hethods, Wintrop Corp., 1980.

[9] H. Schwartz, Computer Communication Network Design and Analysis, Prentice-Hall Inc., 1977.